發布日期:2022-07-14 點擊率:65

系統級流程

視頻處理算法模塊。一旦系統模型完成了調整和驗證,RTL設計師就可以編寫Verilog代碼。高層綜合工具可以從系統代碼生成RTL。但工程師更常見的做法是用RTL代碼手工重新編寫設計。它是設計的解釋而非轉換。即便已用多種驗證測試平臺對RTL實現進行了驗證,采用基于仿真的方法也無法測試全部可能的狀態。

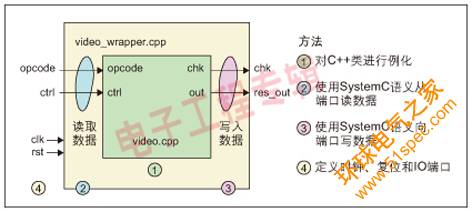

圖1:C/C++系統模型中采用了SystemC封裝器:不用改變C/C++模型就能引入復位和時鐘信號。

設計驗證

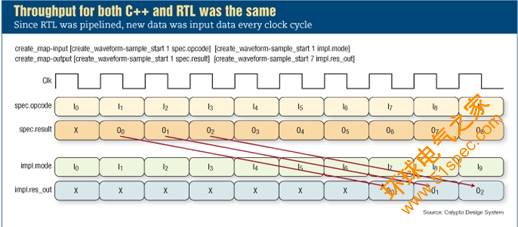

視頻處理器算法塊的RTL實現用了4,559行RTL碼,延時是7個時鐘周期。C/C++系統模型的延時是1個時鐘周期,它是由SystemC“封裝器”引入的。設計團隊隨后規定一組新輸入數據送至每個設計的頻率。因為RTL是管線結構,因此新數據是逐個時鐘周期輸入的。這樣,C/C++和RTL的吞吐量都是1。

圖2:由于RTL是管線結構,新數據是逐個時鐘周期輸入的。因此C/C++與RTL具體有相同的吞吐量。

測試基準的再利用

驗證結果

作者:Jerome Bortolami

高級現場應用工程師

Calypto Design Systems公司